# **Secure Architectures of Future Emerging cryptography**

| State-of-the-Art in Physical Side-Channel Attacks<br>and Resistant Technologies |                                                                                                                                                                                                            |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Deliverable                                                                     | D7.1                                                                                                                                                                                                       |  |  |

| Author(s)                                                                       | Philip Hodgers (QUB), Francesco Regazzoni (USI), Richard Gilmore (QUB), Ciara Moore (QUB), Tobias Oder (RUB).                                                                                              |  |  |

| Version                                                                         | 1.0                                                                                                                                                                                                        |  |  |

| Status                                                                          | Approved                                                                                                                                                                                                   |  |  |

| Date                                                                            | 11 <sup>th</sup> February 2016                                                                                                                                                                             |  |  |

| Classification                                                                  | <ul> <li>White – public</li> <li>Green – restricted to consortium members</li> <li>Yellow – restricted to access list given below</li> <li>Red – Highly sensitive information, access list only</li> </ul> |  |  |

| Access List                                                                     |                                                                                                                                                                                                            |  |  |

HWCommunications Cyber Security and Resilience

INVENTEURS DU MONDE NUMÉRIQUE

Ínría

Università della Svizzera italiana

# **Executive Summary**

This report surveys the current state of the art in physical attacks and countermeasures for cryptographic devices and considers this in relation to the new class of lattice-based implementations. Although lattice-based primitives have been investigated for their resilience against quantum attacks, they will nevertheless require implementation in existing CMOS technology, and, as such, will be susceptible to the same physical attacks as those for existing cryptographies, namely that of side-channel attacks.

As new lattice-based designs emerge, and the number of deployments increase, we expect to see further new attacks described in the literature that exploit the particular characteristics of the lattice-based implementation. Countermeasures to address these specific threats, as they emerge, will be an important area of research going forward. However, we can expect that existing countermeasures such as masking, constant time, randomisation and fault detection will all have an important role to play in lattice-based security.

In terms of performance and security, the implementer will need to carefully consider the use of optimisations, since, for example, the use of lookup tables, early exiting of loops and branching based on secret data, can all lead to a non-constant time of operation. The re-use of libraries, which have been developed with security in mind, can help reduce the likelihood of introducing unintended vulnerabilities in the software context.

Of particular interest on microcontrollers is the use of on-board features, such as true random number generators, which can be used to output pseudo-random and uniformly distributed values. Specialist digital signal processing instructions, such as multiply-accumulate, can also be useful to speed up number theoretic transform calculations for more efficient implementations. For applications where the communication cost matters more than the processing time, it is beneficial to apply compression techniques (e.g. Huffman encoding) to signatures. On-board vector processing units such as AVX or Neon can also greatly increase performance; particularly linear algebraic operations, which are usually well suited for parallelisation. However, care should be taken to consider the potential side-channel leakages when employing any such features.

# **Table of Contents**

| 1                                          | Inti                                                        | ntroduction8                                                    |                                                                                                                                                                                                                                                         |                                                                  |  |  |

|--------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

|                                            | 1.1                                                         | Pur                                                             | pose and Scope                                                                                                                                                                                                                                          | 8                                                                |  |  |

| 2                                          | Inti                                                        | troduction to Physical Attacks9                                 |                                                                                                                                                                                                                                                         |                                                                  |  |  |

|                                            | 2.1                                                         | Attack Classifications9                                         |                                                                                                                                                                                                                                                         |                                                                  |  |  |

|                                            | 2.2                                                         | Timing Attacks                                                  |                                                                                                                                                                                                                                                         |                                                                  |  |  |

|                                            | 2.3                                                         | .3 Power Analysis Attacks                                       |                                                                                                                                                                                                                                                         |                                                                  |  |  |

|                                            | 2.3                                                         | 8.1                                                             | Simple Power Analysis                                                                                                                                                                                                                                   | 11                                                               |  |  |

|                                            | 2.3                                                         | 3.2                                                             | Differential Power Analysis                                                                                                                                                                                                                             | 12                                                               |  |  |

|                                            | 2.3                                                         | 8.3                                                             | Collision Attacks                                                                                                                                                                                                                                       | 12                                                               |  |  |

|                                            | 2.3                                                         | 8.4                                                             | Zero Value Attacks                                                                                                                                                                                                                                      | 13                                                               |  |  |

|                                            | 2.3                                                         | 8.5                                                             | Profiling Attacks                                                                                                                                                                                                                                       | 13                                                               |  |  |

|                                            | 2.3                                                         | 8.6                                                             | Machine Learning Techniques                                                                                                                                                                                                                             | 13                                                               |  |  |

|                                            | 2.4                                                         | Eleo                                                            | ctromagnetic Attacks                                                                                                                                                                                                                                    | 15                                                               |  |  |

|                                            | 2.5                                                         | Fau                                                             | It Attacks                                                                                                                                                                                                                                              | 16                                                               |  |  |

|                                            | 2.6                                                         | Pho                                                             | otonic Emission Analysis                                                                                                                                                                                                                                | 17                                                               |  |  |

|                                            | 2.7                                                         | Cor                                                             | ncluding Remarks                                                                                                                                                                                                                                        | 17                                                               |  |  |

| 3                                          | Cou                                                         | unte                                                            | rmeasures                                                                                                                                                                                                                                               | 19                                                               |  |  |

|                                            | 3.1                                                         | Coι                                                             | Intermeasures Against Timing Attacks                                                                                                                                                                                                                    | 19                                                               |  |  |

| 3.2 Countermeasures Against Power Analysis |                                                             |                                                                 |                                                                                                                                                                                                                                                         |                                                                  |  |  |

|                                            |                                                             | COL                                                             |                                                                                                                                                                                                                                                         | 20                                                               |  |  |

|                                            | 3.2                                                         |                                                                 | Hiding                                                                                                                                                                                                                                                  |                                                                  |  |  |

|                                            | 3.2<br>3.2                                                  | 2.1                                                             |                                                                                                                                                                                                                                                         | 21                                                               |  |  |

|                                            |                                                             | 2.1<br>2.2                                                      | Hiding                                                                                                                                                                                                                                                  | 21<br>22                                                         |  |  |

|                                            | 3.2                                                         | 2.1<br>2.2<br>Phy                                               | Hiding<br>Masking                                                                                                                                                                                                                                       | 21<br>22<br>23                                                   |  |  |

|                                            | 3.2<br>3.3                                                  | 2.1<br>2.2<br>Phy<br>Cou                                        | Hiding<br>Masking<br>vsical Countermeasures for EM Probing and Photonic Emissions                                                                                                                                                                       | 21<br>22<br>23<br>24                                             |  |  |

|                                            | 3.2<br>3.3<br>3.4                                           | 2.1<br>2.2<br>Phy<br>Cou<br>Rot                                 | Hiding<br>Masking<br>rsical Countermeasures for EM Probing and Photonic Emissions<br>Intermeasures Against Fault Attacks                                                                                                                                | 21<br>22<br>23<br>24<br>24                                       |  |  |

|                                            | 3.2<br>3.3<br>3.4<br>3.5                                    | 2.1<br>2.2<br>Phy<br>Cou<br>Rot<br>Aut                          | Hiding<br>Masking<br>vsical Countermeasures for EM Probing and Photonic Emissions<br>untermeasures Against Fault Attacks                                                                                                                                | 21<br>22<br>23<br>24<br>24<br>25                                 |  |  |

|                                            | 3.2<br>3.3<br>3.4<br>3.5<br>3.6                             | 2.1<br>2.2<br>Phy<br>Cou<br>Rot<br>Aut                          | Hiding<br>Masking<br>rsical Countermeasures for EM Probing and Photonic Emissions<br>intermeasures Against Fault Attacks<br>oustness Metrics<br>omatic Application of Countermeasures                                                                   | 21<br>22<br>23<br>24<br>24<br>25<br>25                           |  |  |

| 4                                          | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8               | 2.1<br>2.2<br>Phy<br>Cou<br>Rok<br>Aut<br>Effe<br>Cor           | Hiding<br>Masking<br>rsical Countermeasures for EM Probing and Photonic Emissions<br>untermeasures Against Fault Attacks<br>oustness Metrics<br>comatic Application of Countermeasures<br>ects of Countermeasures on Other Attacks                      | 21<br>22<br>23<br>24<br>24<br>25<br>25<br>25                     |  |  |

| 4                                          | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8               | 2.1<br>Phy<br>Cou<br>Rok<br>Aut<br>Effe<br>Cor                  | Hiding<br>Masking<br>rsical Countermeasures for EM Probing and Photonic Emissions<br>intermeasures Against Fault Attacks<br>oustness Metrics<br>comatic Application of Countermeasures<br>ects of Countermeasures on Other Attacks<br>ncluding Remarks  | 21<br>22<br>23<br>24<br>24<br>25<br>25<br>25<br><b> 27</b>       |  |  |

| 4                                          | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>Lat        | 2.1<br>Phy<br>Cou<br>Rob<br>Aut<br>Effe<br>Cor<br>Line          | Hiding<br>Masking<br>rsical Countermeasures for EM Probing and Photonic Emissions<br>intermeasures Against Fault Attacks<br>oustness Metrics<br>comatic Application of Countermeasures<br>ects of Countermeasures on Other Attacks<br>hcluding Remarks  | 21<br>22<br>23<br>24<br>24<br>25<br>25<br>25<br><b> 27</b><br>27 |  |  |

| 4                                          | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>Lat<br>4.1 | 2.1<br>Phy<br>Cou<br>Rok<br>Aut<br>Effe<br>Cor<br>tice-<br>Line | Hiding<br>Masking<br>rsical Countermeasures for EM Probing and Photonic Emissions<br>intermeasures Against Fault Attacks<br>oustness Metrics<br>comatic Application of Countermeasures<br>ects of Countermeasures on Other Attacks<br>including Remarks | 21<br>22<br>23<br>24<br>24<br>25<br>25<br>25<br>25<br>27<br>28   |  |  |

# SAFEcrypto: D7.1 - State-of-the-Art in Physical Side-Channel Attacks and Resistant Technologies

|   | 4.5 | Concluding Remarks | 32 |

|---|-----|--------------------|----|

| 5 | Cor | nclusions          | 33 |

| 6 | Ref | ferences           | 34 |

# **Table of Figures**

| Figure 2-1 EM scanning platform as defined in IEC 61967-3 [146]15                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-1 A single and dual rail cell. The dual rail cell has complementary input and output lines to balance the power consumption                  |

| Figure 3-2 An unmasked and masked cell. The masked cell has additional mask lines for the inputs and outputs and can process data in a masked state23 |

#### Glossary

- AES Advanced Encryption Standard ASIC Application Specific Integrated Circuit AVX **Advanced Vector Extensions** CED **Concurrent Error Detection** CDT **Cumulative Distribution Table** CML Current Mode Logic CRT **Chinese Remainder Theorem** CMOS Complementary Metal-Oxide Semiconductor DPA **Differential Power Analysis** DEMA Differential Electro-Magnetic Analysis DES Data Encryption Standard DFT **Discrete Fourier Transform** DPA **Differential Power Analysis** DRP Dual-Rail Pre-Charge (Logic) DSP **Digital Signal Processing** EDA **Electronic Design Automation** ΕM Electromagnetic FFT **Fast Fourier Transform** FPGA Field Programmable Gate Array HD Hamming Distance HPC Hardware Performance Counter НW Hamming Weight IC **Integrated Circuit** LFSR Linear Feedback Shift Register LWE Learning With Errors LUT Look Up Table (FPGA) MD4 Message Digest Algorithm MDPL Masked Dual-Rail Pre-Charge Logic NEON Single Instruction, Multiple Data Accelerator for ARM Cortex-A Series NMOS N-Type CMOS NN Neural Network

- NOP No Operation instruction

- NTRU A Lattice-Based Public Key Cryptosystem

- NTT Number Theoretic Transform

- PCA Principle Component Analysis

- PMOS P-Type CMOS

- RAM Random Access Memory

- RC4 Rivest Cipher 4

- RF Random Forest

- R-LWE Ring Learning With Errors

- RNG Random Number Generator

- RSA Rivest-Shamir-Adleman Public Key Cryptosystem

- RSL Random Switching Logic

- SABL Sense Amplifier Based Logic

- S-Box Substitution-Box

- SCA Side-Channel Attack

- SOBER A stream cipher

- SNR Signal-to-Noise Ratio

- SPA Simple Power Analysis

- SVM Support Vector Machine

- TSE Transient-Steady Effect

- WDDL Wave Dynamic Differential Logic

- XOR Exclusive-OR

#### **1** Introduction

#### 1.1 Purpose and Scope

With recent advancements in quantum technology, and the potential that practical quantum computers could become a reality at some future date, there has been renewed interest in the development of cryptographic technologies that are secure from quantum attacks, such as Shor's algorithm for integer factorisation. One promising candidate is cryptography based on the hardness of lattice problems. Although lattice based cryptography offers the prospect of quantum resistance, its deployment will nevertheless require implementation on the same physical platforms as those used for existing non-quantum resistant technologies. For this reason it is very likely that lattice based cryptography will also be vulnerable to the class of attacks known as physical, and in particular, side-channel attacks.

To date there has been little investigation into the resilience of lattice-based implementations from side-channel attacks (in particular advanced techniques) and from physical attacks in general, which an adversary could exploit to reveal information pertaining to the secret key. This document aims to address this issue by surveying the state-of-the-art in physical attacks and countermeasures.

Although most of the existing attacks have been developed for use against non-lattice-based cryptographies, a significant number of these attacks will be directly applicable in the lattice-based context, and it therefore serves as a solid platform to begin our investigations into their security. We will further consider the requirements of a lattice-based implementation and the consequent vulnerabilities that may be exposed because of them.

This document is organised as follows: Section 2 considers the types of attacks and their classifications, summarising the main ways in which physical attacks are carried out, such as power and electro-magnetic (EM) attacks, timing attacks, fault attacks, profiling, and machine learning attacks. Section 3 provides a summary of countermeasure techniques, broadly classified into the areas of masking and hiding. Section 4 then gives an overview of lattice-based implementations, relating this to the vulnerabilities presented in section 2, along with a survey of the current state-of-the-art of attacks and countermeasures for lattice-based cryptography.

#### 2 Introduction to Physical Attacks

In this section, we provide an introduction to physical attacks on cryptographic devices, highlighting the vulnerabilities that make these attacks possible and summarise the most common types.

Cryptography provides confidentiality, integrity, authentication, and non-repudiation of data through the use of cryptographic primitives. A generic encryption algorithm usually takes two inputs, a plaintext and key, and produces a single output of encrypted ciphertext. The opposite transformation of decryption takes as input a key and ciphertext and reconstructs the original plaintext. Following Kerckhoffs' principle, restricting knowledge of the details of an encryption algorithm should not be the means by which security is underpinned, rather the algorithms should be assumed to be known to an adversary. Therefore, security for modern cryptographic schemes is determined through knowledge of the secret encryption key.

Encryption algorithms are carefully designed to be secure from theoretical cryptanalysis, often with mathematical proofs of their hardness against the most powerful of computing adversaries. However, real-world implementations generally require the deployment of these algorithms in some form of low-cost hardware, such as an electronic device that implements the encryption/decryption algorithms and stores, somewhere within itself, the secret key.

For low-cost portable devices, such as smart cards, or mobile computing platforms, such as phones and tablets, an adversary has full access to the device. As such, an adversary is free to not only control what data is passed into the system, perhaps aiding in cryptanalytic attacks, but more importantly an adversary is also able to closely monitor the device, observing its physical properties whilst it performs the cryptographic operations. These physical variables, such as timings required to perform computations, or the instantaneous power consumption during execution of the algorithm, may be acquired using low-cost equipment such as oscilloscopes, making the attacks readily accessible.

The unintended leakage of this side-channel information has a strong dependency on the device being used, the specific operations that are being performed, and on the data being processed. In the case of a cryptographic device, the operations of interest are those that manipulate data that has some relationship, whether direct or indirect, with the secret key. This information can then be compared against a hypothesised model of expected data/key values to determine the value of the secret key and therefore allow an attacker to decipher any past or future communications secured with that key.

# 2.1 Attack Classifications

Physical attacks can be classified according to various criteria. In this study, we follow the classification as described in the book of Mangard *et al.* [1], which is widely considered as the reference in the field of Power Analysis attacks. Here attacks are grouped according to whether they are performed in an active or passive sense and also in relation to the level of invasiveness required.

**Passive Attack:** during a passive attack, the adversary does not tamper with the device, and it continues to operate within its normal parameters. An attack is performed by observing and analysing its physical quantities, such as power consumption or execution time. For example, one can observe the differing time taken to compute a square or multiply operation in an exponentiation operation.

Active Attack: to perform these attacks, the adversary has to manipulate the cryptographic device, by modifying its inputs, its environment, or perhaps both together. The goal is to make the device

behave abnormally, and exploit this behaviour whilst performing the attack. For example, by inducing a fault during the processing of the key, it is possible to reveal whether an individual bit of the secret key is a '1' or a '0'.

Attacks can be further classified depending on the level of tampering required to access the device, i.e. non-invasive, semi-invasive, or fully invasive.

**Non-invasive Attack:** implies that the attacker does not tamper with the device and therefore no trace or evidence of an attack is left behind.

**Semi-invasive Attack:** may include some activities to gain better access to a device, e.g. open the enclosure of a device to enable closer positioning of an electromagnetic probe, but generally we assume that the device itself is not permanently damaged or modified.

**Invasive Attack:** implies the greatest level of tampering, for example the de-packaging of a chip, or soldering wires to points on a circuit. This type of attack clearly requires more time and effort and would often leave evidence that an attack has occurred. This kind of attack may also permanently damage the device under test.

There are multiple leakage vectors that can potentially be exploited, such as timing analysis [2], computational fault analysis [3], acoustic analysis [4], and optical analysis [5]. However, one of the major threats comes from the analysis of power consumption measurements, obtained during power analysis [6] and electromagnetic attacks [7][8][9].

#### 2.2 Timing Attacks

Timing attacks exploit the differences in time required by a device to perform specific operations, such as the non-constant time to execute two different instructions e.g. a division or multiplication, the time needed to fetch data due to a cache memory hit or miss, program behaviour due to branching or conditional statements and optimisations which lead to the skipping of unnecessary operations.

In the particular case of a cryptographic device, these performance characteristics will have a relationship with the secret key and/or the input data. Although it may be assumed that timing characteristics leaked in this manner would only reveal limited information from the device, it was shown by Kocher in [2] that the timings for modular multiply operations in exponentiation operations, and modulo reductions of the Chinese Remainder Theorem (CRT) optimisation in RSA, could lead to the discovery of the entire key. Dhem et al. followed this in [40], where a more generalised approach was demonstrated on a smart card implementation. The approach of Dhem *et al.*, which targeted the squaring operation of Montgomery multiplication, did not require the calculation of partial timings for known parts of the key, and therefore required a less-detailed knowledge of the system.

Timing attacks are not only restricted to localised devices. In [41], Bernstein demonstrated a timing attack of OpenSSL AES, on a UNIX x86 server, across a network. The attack consisted of first profiling the server timing responses with a known key to determine what the maximum timing characteristics were for given plaintext values, and then during the attack phase, by sending plaintexts to the server and comparing the timing responses against the profiled references, thus enabling key byte values to be calculated. The underlying reason for the vulnerability was highlighted as the non-constant timing profile of table lookup operations. At the same time, Brumley and Boneh reported remote timing attacks against OpenSSL in [42]. Here, the attack exploited the factorisation of the RSA modulus by progressively improving the guess of the factor q, by iteratively determining its bit values through timing analysis.

The theoretical use of cache hits and misses was proposed by Page in [43], with cache-timing attacks demonstrated in [44] by Tsunoo *et al.*, where it was shown that DES could be broken using  $2^{23}$

known plaintexts and  $2^{24}$  calculations, with a success rate > 90%. Cache attacks on AES were considered by Bernstein in [41] and more recently in [45] by Tromer *et al.*, where full AES key extraction using DM-CRYPT disk encryption on Linux was accomplished with 800 accesses to an encrypted file, in 65 ms of measurements and 3 seconds of analysis. The OpenSSL library was also attacked in as little as 13 ms, with only 300 encryptions required.

# 2.3 Power Analysis Attacks

Power analysis attacks exploit the fact that electronic devices consume power during their operation. The logic style used to realise the majority of existing integrated circuits is CMOS, and among the reasons that made CMOS a popular choice are its robustness against errors and its reduced power consumption, which is particularly low in its static, non-switching, state.

Combinatorial logic cells of CMOS are built using PMOS and NMOS transistors, arranged in a complementary structure. PMOS transistors are used to compose the pull-up network, whilst NMOS transistors form the pull-down network. The two networks are designed in such a way that they avoid conducting at the same time. For this reason, the static power dissipation of CMOS logic is minimised and relatively constant during steady-state conditions.

When the output of the cell transitions state, there is a brief short-circuit developed that causes a spike of power consumption. However, the predominant power consumption within a CMOS device is generated when the output of the gates transition from either a '0' to '1' or a '1' to '0' logic state. During a '0' to '1' transition, the consumption is primarily due to the charging of the capacitive loads between the internal and external elements of circuitry. Whilst, during the transition from '1' to '0', the stored capacitances are discharged. It is observed that the current drawn by a CMOS transistor is slightly higher when transitioning from a '0' to '1' value.

It is the aggregation of many logic cells charging and discharging together that combine to give a measurable dynamic power signature that is useful in power analysis attacks. As a consequence, the instantaneous power consumption of a cryptographic device has a strong relationship with the data and computational operations being performed.

Two main classes of power analysis attacks are distinguished; simple power analysis and differential power analysis. In the following sections we introduce both types and discuss their properties.

# 2.3.1 Simple Power Analysis

In simple power analysis (SPA), an adversary attempts to derive the secret key using a small set of power traces (possibly as few as one), with the relevant information obtained directly from the trace pattern. A possible target for SPA attacks are cryptographic devices in which the execution path depends on the key. For example, in the case of a software-implementation, branching to different instructions may occur when the secret key, or some component of it, has a specific value. Examples of key-dependent branching can be found in cryptographic routines dealing with operations such as key scheduling, permutations, comparisons, multiplications, and exponentiations.

As a pre-requisite, the attacker must first capture the waveform information in a readable form; a task usually performed with an oscilloscope. This requires precise referencing of the signal, i.e. triggering of the source, and some level of pre-processing, usually in the form of filtering, to remove high frequency noise components, or any other artefacts that would have a significant effect on the pattern's readability. Mounting a successful SPA also requires a detailed knowledge of the instructions or routines being processed on the device, information that is discerned through some prior profiling activity which records, or characterises, the waveform patterns generated by each instruction. Therefore, if a specific instruction (or set of instructions) is executed, dependent on some value of the secret key, it now becomes possible to derive the entire key by simply reviewing the waveform pattern and inferring the key values that are being used.

# 2.3.2 Differential Power Analysis

Differential power analysis (DPA) is particularly accessible from an attacker's point of view since it can reveal the secret key without requiring any detailed knowledge of the device implementation. Typically, only knowledge of the cryptographic algorithm is sufficient. Due to the averaging methods inherent within DPA, it is often successful even when the collected power traces contain considerable amounts of noise.

DPA attacks are based on a divide and conquer strategy, the general approach being that the attacker selects a small portion of the key, makes a hypothesis of its value, and then compares the hypothesis against the measured power traces. By repeating the process, for all sub-key candidates, each sub-key value can be determined and thus the full key recovered.

Power consumption is typically modelled by estimating the number of '1"s in a register via a Hamming weight or Hamming distance power model. Several differing methods of statistically comparing the modelled versus measured power consumptions are commonly used, such as difference of means, distance of means and Pearson's correlation coefficient [10].

A DPA attack can be summarised in the following five steps:

- 1. Choose an intermediate result of the executed algorithm.

- 2. Measure the power consumption.

- 3. Calculate hypothetical intermediate values.

- 4. Map intermediate values to hypothetical power consumption values.

- 5. Statistically compare the hypothetical power values with the measured power traces.

To improve DPA attacks, the adversary can target several intermediate values and hypothesise all of them. Typically, the number of values used while formulating the hypothesis is used to classify the specific attack. Thus the standard DPA is referred as a first-order attack, whilst attacks using more values are called higher-order attacks. The most common higher-order DPA uses a hypothesis based on two points and is called second-order DPA, as introduced in [11], [12] and [13]. The working principles of higher-order DPA's are the same as those for first-order DPA, with the exception being that a preliminary pre-processing phase is often required. This pre-processing combines, by means of some joint function, a number of points to hypothesise intermediate values, which can then be compared against the power measurements.

One potential drawback of DPA can be the large number of samples needed to mount an effective attack, which can require a significant time to complete. Thus an adversary will usually need to have full, unrestricted, access to the device during this phase of the attack.

# 2.3.3 Collision Attacks

Collision attacks target the scenario where two encryptions, computed using differing inputs and an unknown key, can generate the same intermediate values. The collision can be exploited if an adversary is able to measure the power consumption of the two encryption operations that create this event. Since it is only possible for two inputs to generate a collision for certain key values, each identified collision enables the attacker to reduce the search space for key recovery.

Schramm *et al.* introduced the attack in the context of power analysis in [14] and [15], where intermediate values of DES and AES were targeted using power analysis to recover the key. Linear and algebraic collision attacks were introduced by Bogdanov in [16] and [18], and by Bogdanov and Pyshkin in [17], with attacks on AES. Their approach further reduced the number of measurements required to detect collisions, and therefore recover the key.

#### 2.3.4 Zero Value Attacks

Zero value attacks exploit the fact that certain cryptographic operations that process zero values can cause the leakage of information that reveals the secret key. In [19] Golić and Tymen showed that a zero value attack could overcome the multiplicative masking countermeasure of an AES block cipher; since multiplying a random mask with a zero value will result in the same, unmasked, zero value. Whilst in [20] Goubin showed that scalar multiplication is insufficient to protect elliptic curves against DPA attacks. Their attack supposes that the curve E(K) contains a special point  $P_0 \neq \Theta$ , such that one of the (affine or projective) co-ordinates is equal to 0 in K. Where this is the case, key bit guesses are shown to result in noticeable power consumption peaks, enabling the key to be recovered. Akishita and Takagi extended the attack in [21], where it was pointed out that even if a point lacks a zero-value co-ordinate, the auxiliary registers might still have zero-values, thus enabling an attack.

# 2.3.5 Profiling Attacks

Profiling attacks were first introduced by Fahn in [22] with Inferential Power Analysis (IPA), an attack against DES on a smartcard, and later with the template attack of Chari *et al.* in [23], an attack against an RC4 implementation on a smart card. These approaches require an identical test device for which the attacker knows the key and plaintext sequence. The device under test is supplied successive plaintexts, with the recorded power consumption values used to compile a power profile for the device. This profile can subsequently be compared with the measured power consumptions of an identical device to determine which key values were used in the target device. In [24], Rechberger and Oswald, and subsequently Gierlichs in [25], looked at different ways to find the points of interest in the power trace to further improve the efficiency of the template. The profiling phase of a template attack necessitates an intimate knowledge of the implementation in order to enable the operations to be profiled accurately, which may require a large number of power traces to be gathered. However, if this level of information is available, the template attack can be a very powerful side-channel attack, since it can potentially reveal the key with as little as one power trace, as shown in [23].

Another, more recent, example is the profiling of hardware performance counters (HPCs), investigated by Bhattacharya and Mukhopadhyay in [26], as a means of obtaining side-channel information. The author's targeted 1024-bit RSA on an Intel platform by monitoring the state of the HPCs to determine the number of branch misses on the square any multiply operations of the Montgomery exponentiation algorithm. By comparing the online HPC values against previously profiled HPC simulation values, they were able to successfully determine the RSA key bit values.

# 2.3.6 Machine Learning Techniques

The application of machine learning as a method to perform SCA is a relativity new idea with only a few papers exploring the concept. To date most of the work has centred on the use of support-vector machines to perform attacks, as well as random forests. Comparison between different machine learning attacks that have currently been used is difficult as they have been applied to different architectures and have each employed differing attack models.

# 2.3.6.1 Supervised Learning

Supervised learning requires labelling of the data, i.e. knowledge of what the correct class for a particular input should be. The learner is then trained by testing the output of the algorithm against the expected value. A cost is added when the learner incorrectly identifies a sample and this is repeated iteratively until the learner can identify the sample, or until no significant improvement in identification occurs. In most SCA labelling the data with the correct key is fairly trivial and the majority of research into using machine learning for SCA has been through the use of supervised

learning. However, in these cases the features selection stage has either been manual or had limited processing carried out on the data. It is here that unsupervised learning has true potential, to identify suitable features from traces that have countermeasures and where leakage identification is not trivial.

The specific machine learning algorithm used is often less important for a successful attack than the feature selection and data set size. That being said, there are differences in how the algorithms operate; i.e. whether the algorithm can handle non-linear relationships and whether the resulting model is black box or can easily be interpreted.

# 2.3.6.2 Support Vector Machines (SVM)

SVMs have been the most widely studied algorithm for SCA. Such attacks are described in the works of [27], [28] and [29]. SVMs typically employ one-versus-all classification and use multiple binary classifiers to separate multi-class data. Dividing the problem into multiple binary classification problems is the most common way to approach multi-class problems, for a problem with M classes this leads to M classifiers. This makes SVMs more suited to attacks using a bit or Hamming weight model, since a byte model would require 256 classifiers, as described by Lerman *et al.* in [30].

# 2.3.6.3 Random Forest (RF)

The authors in [30] also explored the use of RF classifiers to attack DES. RF classifiers use an ensemble of decision trees to classify data. A simple decision tree can lead to overfitting of training data and poor generalisation on test data. To overcome overfitting RFs average over multiple decision trees, each trained on a random subset of the features given.

# 2.3.6.4 Neural Networks (NN)

NNs map input data to output classes using one or more hidden layers. These hidden layers can learn non-linear relationships between the data, NNs are inherently multi-class. "Shallow" NNs, those with one or two hidden layers, perform similarly to SVMs and are mathematically similar. Deep neural networks, those with a large number of hidden layers, have only recently become viable due to the large computational cost in training such a network. Gilmore *et al.* [31] used a two stage neural network to attack a masked version of AES.

# 2.3.6.5 Unsupervised Learning

Unsupervised learning does not require any labelling of data, instead clustering algorithms attempt to group data based solely on similarities found within the data. It is often possible to label these clusters afterwards and then use the clustered data to carry out supervised learning. Principle component analysis and independent component analysis are two methods used for unsupervised learning that use the statistical properties of the samples to group data. Chou *et al.* [32] use an unsupervised learning model for SCA; this paper is an initial exploration of the topic, with room for more extensive research in this subject area.

Principle component analysis (PCA) has been used as a pre-processing technique for DPA [33]. PCA has been used in numerous fields extending beyond that of SCA, with the assumption that the highorder eigenvectors contain all the relevant information, with the low order eigenvectors containing noise, enabling the dimensionality to be reduced, thus increasing the SNR of the desired features. This theory however has been challenged in [34] and [35], where it was shown that when information was clustered in a localised small set of points in a large data set, then this information was actually in a particular set of low order eigenvectors. In SCA the points of interest are typically a small localised set amidst a large number of uninteresting points; this was tested and shown to be an effective technique in [36], with the theory further developed in [37]. The application of PCA is still an active area of research and advances in this field may yield further insights into how to improve its usage with SCA. Moreover, it has only been put to limited use as a feature extraction technique for use with machine learning [29] and for whitening in [31].

#### 2.4 Electromagnetic Attacks

Electromagnetic (EM) attacks were first introduced in the literature in [7], as the differential electromagnetic analysis (DEMA) technique. DEMA is a variant of the DPA attack of Kocher [6], differing in the method of obtaining the power consumption readings. In EM attacks, an electric or magnetic field probe is used to convert the fields generated by current flows from within the device circuitry into voltage signals, for recording with an oscilloscope. EM fields are usually sensed with near field probing methods. However, as Agrawal *et al.* showed in [9], it is also possible to use far field antennas, with AM demodulation techniques, to extract the side-channel information.

The techniques of measuring side-channel EM emissions are not new. Research in the 1960's was undertaken by the US Department of Defence in the TEMPEST programme. This came after the discovery at Bell Labs that their electro-mechanical signalling machines, used for covert communications by the US army and intelligence services, were found to emanate EM pulses that could be used to reveal which characters had been typed at the terminals [38]. Later, other EM side-channel attacks were developed, relating to the reconstruction of computer monitor screens by capturing the vertical and horizontal scan patterns of cathode ray tubes.

An EM acquisition has several attributes that may offer advantages over that of traditional power analysis attacks.

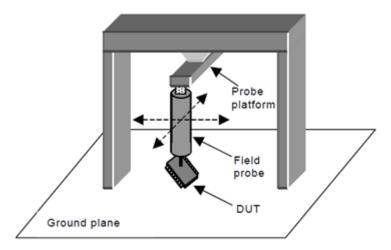

*Reduced Invasiveness:* In a power analysis attack, the adversary usually attaches a resistive load between the power supply, or ground, of the target device. Measurements are then recorded using an oscilloscope, registering the changes in the voltage drop across the resistor as the current flow drawn by the device fluctuates. The resistor may require soldering in-circuit, leaving permanent evidence of the attack. In contrast, the electric and magnetic fields radiating from a device permit measurements to be taken with a non-contact probe. Skorobogatov showed in [39] that with the use of invasive techniques, such as decapsulation, that it is possible to gain closer access to the IC core. With modern sensitive EM probes, and through use of pre-amplifiers, placing the probe tip on the chip surface will often provide sufficient signal strength to mount a successful attack. The EM probe can therefore potentially offer a fully non-invasive approach to side-channel measurement. A typical EM measurement is shown in figure 2-1.

Figure 2-1 EM scanning platform as defined in IEC 61967-3 [146].

*Improved Localisation:* In a power analysis attack, the position of the load resistor is fixed, with the power consumption of the entire device generally being recorded. This macroscopic power

consumption consists of contributions, not only from the targeted encryption processing core, but also from other regions of the device that may be carrying out other tasks or generating electronic noise from unrelated system switching activities. This statistically unrelated information can lead to anomalies in the side-channel analysis, a feature termed as 'false peaks' by Gandolfi *et al.* in [8]. In contrast, the EM probe may be positioned at any desired location, and with the use of a high resolution, fine-tipped probe, the power consumption contributions from a small localised area of a device may be recorded, thus minimising the power consumption contributions from other unrelated areas of the device.

The quality and strength of the acquired signals, with respect to noise, is an important factor in determining the success of a side-channel attack, although pre-processing techniques such as alignment, averaging and pattern matching can be used to improve the result.

*Enhanced Pattern Matching:* The localised nature of EM power consumption measurements can also assist with pattern extraction techniques, since the acquired data will more closely resemble the characteristic power consumption patterns that are being profiled. For example, the ten successive rounds of AES will often produce the corresponding pattern of ten processing peaks on the oscilloscope's display. Passing an EM probe across the surface of a device that is processing an encryption algorithm will show a varying pattern at different locations across the IC's surface. The areas which display the clearest pattern of the ten rounds of AES will have the best signal-to-noise characteristics and thus offer the most advantageous position to mount the attack.

# 2.5 Fault Attacks

In fault attacks, the adversary purposely induces a fault and exploits the erroneous behaviour of the circuit to gain some information about the secret key. These errors are typically transient in nature, meaning that their effects are reversible. As such, once the fault has propagated through the circuit, the device will continue to operate normally. This approach is advantageous since if the device is not permanently damaged, the attacker can continue to perform many repeated experiments, sufficient to generate and observe the desired effects.

Although the chance of faults occurring spontaneously within a device are very small, Anderson and Kuhn showed in [46] and [47] that faults may be intentionally introduced in smart cards by varying the supply voltage, system clock speed or ambient temperatures. A further class of invasive attacks were introduced by Skorobogatov in [5] and [39], with the use of destructive ion beams and semipermanent optical fault injection techniques; the faults being shown to induce effects such as changing the values of internal registers, incorrect branching of the program or the skipping of program instructions.

Fault attacks presented in the literature target both public and private key algorithms. The attack of Boneh *et al.* [48] targets the Chinese remainder theorem computation of the RSA signature scheme and is particularly efficient since, to be successful, it requires only one correct and one faulty signature. Fault analysis techniques were subsequently applied to attacks on other signatures schemes in [49], [50] and [51].

Among the attacks that target block ciphers, the attacks on AES are of particular interest. One example is the work in [52], which describes a differential fault attack against the substitution permutation network. The work of Kim and Quisquater in [53] targets the key schedule of AES, and to be successful requires only two faults to occur in the 9th round. Concerning active attacks, the most common is the fault injection attack of [54].

Fault attacks relating to stream ciphers were first introduced by Hoch *et al.* in [55], where the linearity of the LFSR component is exploited, with attacks on LILI-128 and SOBER. An attack against RC4 is also demonstrated, with random faults introduced into the S-table and the first output byte of RC4 after initialisation is targeted.

A description of several ways to induce faults in cryptographic devices is reported in [56] by Barenghi *et al.* The authors classified the attacks in two main classes; low cost, and high cost (with the differentiator being a cost of more than 3000 \$USD for the attack to be carried out). An additional ranking of the attacks is then provided, based on the skills needed by the adversary, which can be low, moderate, high, or complete. Among the simplest attacks (which are low cost and that can be carried out with limited skills) are underfeeding and heating. Both approaches were shown to be an effective way to successfully mount a fault attacks.

The resistance against a successful fault attack can be significantly affected by the shrinking of the technology and through the use of aggressive power saving techniques. For example, in [57], Barenghi *et al.* describe an in-depth characterisation of a chip implementing AES, manufactured with a 65nm low power library and working in the subthreshold voltage range. The authors show that it is possible to inject faults that would enable an attack to be performed against the cipher. The authors also addressed the problem of predicting such faults at design time, employing standard EDA tools. They concluded that it is possible to predict which lines are more likely to fail, through a static time analysis.

An attack on block ciphers, using the insertion of clock glitches to induce faults, was proposed by Ren *et al.* in [58]. Their transient-steady effect (TSE) attack exploits the fact that a combinatorial circuit will often have a transient state before transitioning to a correct output state. The attack is performed by injecting a clock glitch into the system, with the output state monitored to capture any key related information which is briefly leaked during the transient stage of the combinatorial circuit's operation. The authors state that an advantage of this attack approach, over other fault attacks, is that it does not require a large number of encryptions in order to build the statistical model.

# 2.6 Photonic Emission Analysis

In photonic emission analysis, such as the work of Schlösser *et al.* in [147], the backside of an IC can be observed and photon emissions recorded with a very high spatial resolution. Although the described attack was made more accessible through thinning of the backside substrate, the authors pointed out that many advanced security IC's, such as those contained within modern smart cards, tend to have thinner substrates. In any case, more advanced InGaAs cameras, which are sensitive above a  $1\mu$ m wavelength, are able to detect the photonic emissions readily, since, at these frequencies, the silicon becomes transparent with respect to their propagation.

The approach of photonic emission analysis, although invasive and requiring a custom scanning platform to be developed, has the potential to enable the determination of values held within individual transistors on a device. The authors demonstrate that it is possible to read s-box values directly form a composited image of the photon emissions of SRAM memory cells, in a manner equivalent to a simple power analysis.

It is claimed by the authors that the cost of such a system is comparable to that of a mid-range oscilloscope. However, due to the bespoke nature of its construction, and level of invasiveness required (the device needs to be completely removed from the system), it is considered to be a more specialised approach for mounting an attack.

# 2.7 Concluding Remarks

Physical attacks have been an active research topic for nearly 20 years now, not only because of the high level of threat posed by such attacks, but also because they are constantly evolving. As soon as new countermeasures are published, then new attacks begin to be developed, and whilst there continues to be a strong incentive to break protected systems, this activity will surely continue.

As we have seen, there are a large number of possible attack vectors that the cryptographic engineer needs to be aware of. Over time these attacks have become more accessible to the adversary, with the continued lowering in cost of equipment such as oscilloscopes and probes. The processing of large side-channel data sets may also require significant computing resources. With the advent of cloud services, it now becomes much easier for a scaleable, on-demand, processing resource to be applied, without investment in upfront infrastructure costs.

The power and sophistication of attacks has improved through the advancement of analysis techniques, developing from simple comparators such as the difference of means, through differential analysis using Pearson's correlation, to the more recent mathematical treatments and statistical methods such as information analysis. As improvements in the sophistication of attacks continue, both new and existing countermeasures will require ongoing evaluation, ensuring that they continue to offer the required levels of protection. Indeed, there is now a wide array of countermeasures available for the cryptographic engineer to choose from, many of which can be used in combination, supporting a multi-layered approach to their implementation. In the next section, we will consider the various countermeasures that have been proposed to combat the ongoing threat from physical attacks.

#### **3** Countermeasures

The implementation of cryptographic algorithms onto electronic devices has the unfortunate consequence that it also leads to the unintentional leakage of side-channel information, exposing vectors of attack that can reveal the secret key and thus compromise system security. Countermeasures are the means by which cryptographic devices are protected in order to minimise leakage and thwart attacks. In this section we present the general ideas behind the various countermeasures and their implementation.

Power analysis is generally considered the most powerful physical attack presented so far. It requires little information about the implementation, with knowledge of the encryption algorithm usually sufficient to mount a successful attack. As such, this research topic has attracted significant interest and we therefore start with a survey of power analysis countermeasures and dedicate a large portion of this chapter to this topic.

#### 3.1 Countermeasures Against Timing Attacks

As discussed in section 0, timing attacks exploit the differences in the time taken to process information that has some relationship to the secret data. Vulnerabilities have been described in the literature for both implementations in the hardware and software contexts and for the various standard public key and symmetric encryption algorithms. For the designer, one of the main pitfalls to be weary of is that of optimisation. Well-intentioned efforts at improving performance through the use of pre-computed lookup tables, or early exits from loops, for example, whilst reducing execution time, will often lead to the leakage of timing information. Care should also be taken when considering the implementation of a given design across differing platforms, since leakages are commonly device specific and closely related to the physical characteristics of the device.

There have been various countermeasures proposed to thwart timing attacks. As already discussed in section 3.2.2, masking countermeasures will change the intermediate values, so that even if their values are leaked, they will not directly reveal the key data. However, their implementation cost may be high and therefore impractical on the constrained device with limited resources.

In Kocher's seminal paper on timing attacks [2], it was discussed that one option is to try and make all operations execute in a constant time. Although conceptually straight-forward, in practise this may not be so easy to accomplish. As Kocher noted, this was a difficult task because of issues such as compiler optimisations, RAM cache hits, and variances in instruction timings; since these aspects are generally outside the control of the designer, particularly in the context of a software implementation. Kocher further suggested the possibility of inserting random delays (with a clockskipping countermeasure later patented [83]). However, it was noted that this approach had the effect of adding noise, which could be overcome by gathering more traces to average out its effect; with the number of samples required increasing approximately as the square of the timing noise. Kocher recommended the use of blinding to protect RSA, a concept originally proposed by Chaum in [84], coupled with the additional masking of the exponent with a random value before each modular exponentiation.

In [40], where Dhem *et al.* targeted the squaring operation of the Montgomery multiplier of RSA, it was suggested that a simple fix was to make the multiplier operation constant time by adding an additional subtraction operation, even if the result was to be discarded. It was pointed out, however, that the smart card implementation, broken in their demonstrated attack, already included this countermeasure, but that the implementation had a flaw, such that there was still a small time variation between the timings of whether the result was discarded or copied at the end of the

operation. This demonstrates clearly that careful consideration must also be given to the implementation of countermeasures. At the same time, in [85], Schindler proposed the use of dummy operations within the Montgomery multiplier in order to hide the leakage of timing information.

In the context of smart card implementations, the option to disable cache flushing, was proposed by Page in [86].

The work of Tromer *et al.* in [45] considers various countermeasures against cache attacks. Some possible options are:

- 1. Avoid the use of memory accesses by replacing lookups with equivalent logical operations. This is a possibility for algorithms such as AES. However, there will be a performance tradeoff.

- 2. Use of bit-slicing approach, such as described in [87].

- 3. Use of a cache no-fill mode, where memory is accessed from the cache during a hit and serviced from memory when there is a cache miss.

- 4. Dynamic table storage, where the contents of the table lookup is cycled around in memory during encryption operations in order to de-correlate it.

For some guidance on generic coding standards, in relation to cryptographic implementations in software, the reader is referred to the resource of [88]. For example, in the context of timing attacks, it is recommended:

- 1. Do not compare secret values on a byte-by-byte basis

- 2. Avoid branching predicated on secret data

- 3. Avoid the use of lookup tables indexed by secret data

- 4. Avoid loops that are bounded by a secret value.

The software implementer can leverage existing libraries, such as NaCl [89], written specifically with security in mind.

Some processors also include custom instruction sets dedicated to cryptography, such as the AES-NI instructions [90], included in the Intel processors since the Westmere architecture. The AES-NI instruction set consists of seven instructions that perform several portions of the AES algorithm. AESENC performs ShiftRows, SubBytes, MixColumns and AddRoundKey, whilst AESENCLAST processes the last round of the algorithm, skipping MixColumn. Similarly, the decryption is accelerated by AESDEC and AESDECLAST. Two instructions are also used for fast key generation, namely AESKEYGENASSIST and AESIMC. A seventh instruction, PCLMULQDQ, aids in carry-less multiplication. According to the manufacturer [90], use of these processor instructions can boost performance, ranging from a factor of x2 to x10, over that of purely software-based implementations. Since these instructions enable an implementation avoiding table lookups, it is also claimed in [91] that security against cache timing attacks is improved.

#### **3.2** Countermeasures Against Power Analysis

The main goal of a countermeasure against power analysis attacks is to make the power consumptions independent from the processed secret data. It is important to note that it is not necessary to reach independence from all processed data in the device, but rather specifically from data that would allow the attacker to verify the intermediate secret values, for example, from the inputs or outputs of the s-boxes in AES, or the values of the exponentiation of RSA.

Counteracting SPA is a more straight-forward prospect; since the attacker has to visually explore the traces, it is sufficient to protect the values directly related to the secret key that affect the program

execution or its behaviour. For example, concerning conditional branches, if the programmer is able to ensure the absence of conditional branching that depends on the secret data, the adversary has limited chances to gain useful information from the inspection of the power traces. Another approach is to increase noise levels to try and hide the signals during the data dependent processing.

Protecting a device from DPA, by contrast, is a much more difficult task, since this attack uses advanced statistical techniques to extract information from a large number of traces.

Countermeasures can be classified into two broad groupings: those that aim to hide the data and those that are designed to mask the data [1]. These concepts are generally valid in both the hardware and software contexts and depend upon the particular methodology adopted to achieve protection. Furthermore, although the two approaches are independent from one another, they are complimentary and thus may be combined, providing a multi-layering of countermeasure implementations.

#### 3.2.1 Hiding

Fundamentally, a hiding countermeasure does not change the intermediate data values that are processed in an encryption algorithm, rather it attempts to hide those values in amongst the other processing activities. Typically, hiding is achieved in one of two ways: by randomising the power consumption or by making the power consumption constant during all processing operations.

A random power consumption can be achieved by changing, in each iteration of the algorithm, the time at which a given cryptographic operation is executed. If the targeted intermediate value is processed in a differing instant in time, then the attack will become more difficult since a more complicated trace re-alignment step is required. Two possible ways for randomising the power consumption are the random insertion of dummy instructions and the shuffling of the operations. Both methods may also be combined. This temporal misalignment between successive side-channel acquisitions reduces the effectiveness of an adversary's statistical analysis.

Pre-processing techniques such as integration [59] can assist in reducing this effect, but are only effective to a certain extent, limited by  $\sqrt{l}$ , where l is the length of the integrating window [1]. In [60] and [61] Homma *et al.* proposed a technique called phase-only correlation to improve the realignment of traces. An alternative approach, based on frequency analysis, was published by Gebotys *et al.* in [62], where the captured data was first transformed into the frequency domain using a discrete Fourier transform (DFT), creating a series of spectrograms for the analysis. Although this approach overcomes misalignments, since it is time-shift invariant, the size of the spectral windowing has an effect on the noise, and a balance therefore needs to be made between a large enough window to capture the common processing operations and the desire to minimise the window width, therefore avoiding the inclusion of unnecessary noise, as considered by Hodgers *et al.* in [63]. Pattern matching techniques that can identify the processing region of interest, and realign the traces based on those characteristic features, is therefore another possible method open to an attacker, as described in [64].

The use of random insertions can have a significant impact on the performance of the system, since dummy operations are purely redundant processing activities. It also offers only limited protection, since the attacker can potentially take many measurements to average out the effects of the randomisation.

The second approach for counteracting power analysis attacks aims at equalising the power consumed by each instruction of the device. As Agrawal *et al.* observed in [9], the instructions of a processing device, such as a micro-controller, can use differing amounts of power with some 'bad instructions' consuming significantly more power than others. Approaches in software to minimise the variance of the power consumption include techniques such as choosing processor instructions with similar power consumption profiles. Hardware approaches have focussed on features such as

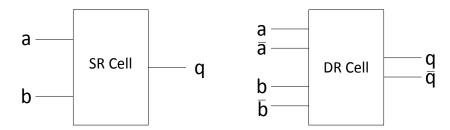

incorporating on-board power filters, to reduce exploitable power leakage, through to adding noise generating engines on the device to increase the noise floor. An alternative approach has focussed on implementations at the level of the logic cells, namely with the use of dual-rail pre-charge (DRP) logic styles. DRP uses two wires that are complementary for each signal, as shown in figure 3-1. Care is taken on the interconnection between DRP cells to ensure that the capacitive loads are balanced, as this aspect tends to determine the overall effectiveness of the system.

In [65] Tiri *et al.* proposed the use of Sense Amplifier Balanced Logic (SABL) to provide resistance against DPA. SABL has the property that it charges and discharges the same capacitance (internal and external) every clock, regardless of its state. This was followed with proposals for Current Mode Logic (CML) in [66], [67] and [68], and Wave Dynamic Differential Logic (WDDL) in [69]. WDDL uses standard cells, avoiding the time and cost of implementing a full custom design, though its capacitive balancing, and therefore DPA resistance, is not perceived to be as good as SABL.

Figure 3-1 A single and dual rail cell. The dual rail cell has complementary input and output lines to balance the power consumption.

#### 3.2.2 Masking

Masking is a technique based on secret-sharing, where the original message is divided into parts called shares and the message can only be reconstructed if a sufficient number of shares is known. The idea of applying secret-sharing to counteract power analysis was first proposed by Chari *et al.* [70] and further improved by Messerges in [11]. With masking, the intermediate values that are processed generate a power consumption that is uncorrelated with the secret key, even though the power consumption characteristics of the device remain unchanged.

When considering an algorithm for masking, such as AES, the linear operations of ShiftRows, MixColumns and AddRoundKey are all easily dealt with since a liner operation has the property of  $f(x \oplus m) = f(x) \oplus f(m)$ . However, for the non-linear SubBytes operation,  $S(x \oplus m) \neq S(x) \oplus S(m)$ . For this reason, masking schemes can be complex and require careful consideration during their design. It is possible to divide the masking schema in two groups, based on the operations used to calculate the masked value, namely Boolean and arithmetic masking. Boolean masking uses a bitwise exclusive-or operation to mask the intermediate value and is particularly suitable for masking linear functions of cryptographic algorithms. Arithmetic masking uses operations such as modular addition or modular multiplication to mask the intermediate values and is particularly suitable when used to mask the non-linear functions, but for other operations it has one major problem; not all the intermediate values can be masked.

An aspect that can cause masking schemes to become complicated is the potential requirement to switch between Boolean and multiplicative masking. Akkar and Giraud proposed an efficient method to facilitate this process in [71]. Multiplicative masks do have a major disadvantage in that they cannot conceal the intermediate value if it is zero. Oswald *et al.* proposed a scheme that took this weakness into account using a combination of additive and multiplicative masks in [72].

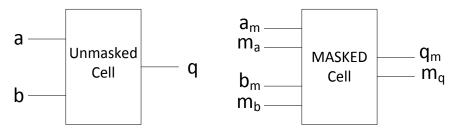

There have also been developments in the hardware implementation of masking, with the introduction of masked logic styles by Trichina [73]. This approach employs the principle that, since a

Boolean mask is a linear operation, the values can be processed in a masked cell without requiring the unmasking of the data. The encryption algorithm can therefore be implemented in an unmasked manner, with the masking taken care of automatically at the logic level. The implementation requires an additional line to carry the mask bits associated with each input and output from the cell, as shown in figure 3-2.

Figure 3-2 An unmasked and masked cell. The masked cell has additional mask lines for the inputs and outputs and can process data in a masked state.